単一光子検出器80%の効率のボトルネックを突破した

単一光子光検出器コンパクトで低コストという利点から、量子フォトニクスや単一光子イメージングの分野で広く使用されているが、以下のような技術的なボトルネックに直面している。

現在の技術的制約

1. CMOSおよび薄接合SPAD:集積度が高くタイミングジッタが低いものの、吸収層が薄く(数マイクロメートル)、近赤外領域でのPDEが制限され、850 nmでは約32%にとどまります。

2. 厚接合型SPAD:数十マイクロメートルの厚さの吸収層を備えています。市販品は780nmで約70%のPDEを実現していますが、80%を超えることは非常に困難です。

3. 読み出し回路の制限:厚接合SPADでは、高いアバランシェ確率を確保するために30Vを超えるオーバーバイアス電圧が必要です。従来の回路では、68Vの消光電圧を使用しても、PDEは75.1%までしか増加しません。

解決

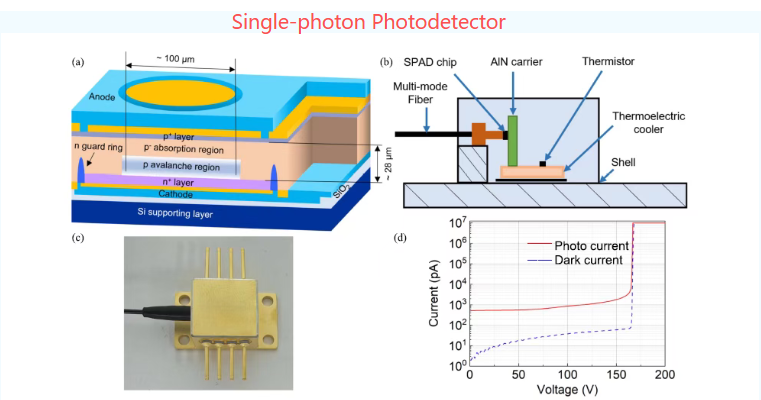

SPADの半導体構造を最適化します。裏面照射設計:入射光子はシリコン中で指数関数的に減衰します。裏面照射構造により、光子の大部分が吸収層で吸収され、生成された電子がアバランシェ領域に注入されます。シリコン中の電子のイオン化率は正孔のイオン化率よりも高いため、電子注入によりアバランシェの発生確率が高くなります。ドーピング補償アバランシェ領域:ホウ素とリンの連続拡散プロセスを使用することで、浅いドーピングを補償し、結晶欠陥の少ない深い領域に電界を集中させ、DCRなどのノイズを効果的に低減します。

2. 高性能読み出し回路。50Vの高振幅クエンチング、高速状態遷移。マルチモード動作:FPGA制御のクエンチング信号とリセット信号を組み合わせることで、フリー動作(信号トリガー)、ゲーティング(外部ゲート駆動)、ハイブリッドモード間の柔軟な切り替えが実現されます。

3. デバイスの準備とパッケージング。SPADウェハプロセスを採用し、バタフライパッケージを使用する。SPADはAlNキャリア基板に接合され、熱電冷却器(TEC)上に垂直に取り付けられ、サーミスタによって温度制御が行われる。マルチモード光ファイバーは、効率的な結合を実現するために、SPADの中心に正確に位置合わせされる。

4. 性能校正。校正は、785 nmピコ秒パルスレーザーダイオード(100 kHz)と時間デジタル変換器(TDC、分解能10 ps)を使用して実施した。

まとめ

本研究では、SPAD構造(厚接合、裏面照射、ドーピング補償)の最適化と50V消光回路の革新により、シリコンベース単一光子検出器のPDEを84.4%という新たな高みへと押し上げることに成功した。市販製品と比較して、その総合性能は大幅に向上しており、超高効率と柔軟な動作が求められる量子通信、量子コンピューティング、高感度イメージングなどのアプリケーションに実用的なソリューションを提供する。本研究は、シリコンベース単一光子検出器のさらなる発展のための確固たる基盤を築いた。単一光子検出器テクノロジー。

投稿日時:2025年10月28日