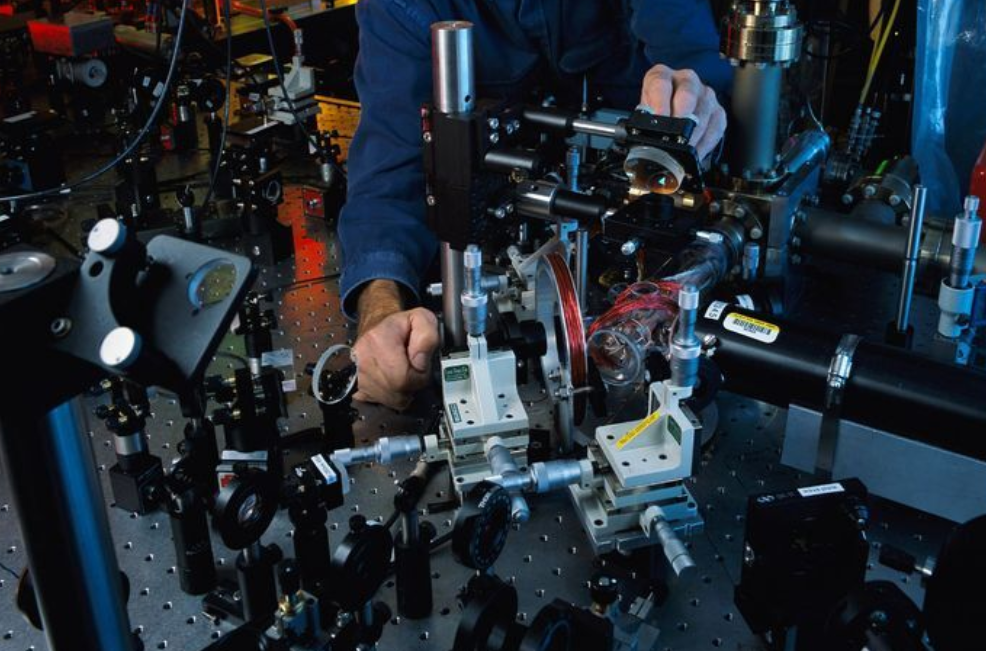

CPOの進化と進歩光電子工学共同包装技術

光電子共同パッケージングは新しい技術ではなく、その開発は1960年代にまで遡りますが、現時点では、光電子共同パッケージングは、光電子デバイス1990年代には、光通信モジュール業界では、光電共同パッケージングが台頭し始めました。今年は、高コンピューティング能力と高帯域幅の需要が急増し、光電共同パッケージングとその関連技術は再び大きな注目を集めています。

技術開発においては、各段階もそれぞれ異なる形態をとり、20/50Tb/s 需要に対応する 2.5D CPO から、50/100Tb/s 需要に対応する 2.5D Chiplet CPO まで、最終的には 100Tb/s 速度に対応する 3D CPO を実現します。

2.5D CPOパッケージは、光モジュール光電変換モジュールとネットワークスイッチチップを同一基板上に配置することで、配線距離を短縮し、I/O密度を高めました。さらに、3D CPOは光ICを中間層に直接接続することで、50um未満のI/Oピッチの相互接続を実現しました。その進化の目標は非常に明確で、光電変換モジュールとネットワークスイッチチップ間の距離を可能な限り短縮することです。

現在、CPOはまだ初期段階にあり、歩留まりの低さやメンテナンスコストの高さといった問題を抱えており、市場でCPO関連製品を完全に提供できるメーカーはごくわずかです。Broadcom、Marvell、Intel、そしてその他少数の企業のみが、完全に独自のソリューションを市場に提供しています。

Marvellは昨年、VIA-LASTプロセスを採用した2.5D CPOテクノロジースイッチを発表しました。シリコン光チップを加工した後、OSATの加工能力を用いてTSVを加工し、さらに電気チップをフリップチップでシリコン光チップに付加します。16個の光モジュールとスイッチングチップMarvell Teralynx7をPCB上で相互接続することでスイッチを構成し、12.8Tbpsのスイッチング速度を実現します。

今年の OFC では、Broadcom と Marvell も、オプトエレクトロニクス共同パッケージング技術を使用した最新世代の 51.2Tbps スイッチ チップを実演しました。

Broadcomの最新世代CPOの技術的詳細を見ると、CPO 3Dパッケージはプロセスの改良によりより高いI/O密度を実現し、CPOの消費電力は5.5W/800Gと非常に高いエネルギー効率比を実現しています。同時に、Broadcomは200Gbpsと102.4T CPOという単一の波も突破しています。

シスコはCPO技術への投資を拡大し、今年のOFCでCPO製品のデモンストレーションを実施し、CPO技術の蓄積と、より統合されたマルチプレクサ/デマルチプレクサへの適用を示しました。シスコは、51.2テラビットスイッチでCPOのパイロット導入を実施し、その後、102.4テラビットスイッチサイクルで大規模導入を行うと述べています。

Intel は長年にわたり CPO ベースのスイッチを導入しており、近年では Ayar Labs と連携して、共同パッケージ化されたより高帯域幅の信号相互接続ソリューションの研究を続け、オプトエレクトロニクス共同パッケージおよび光相互接続デバイスの大量生産への道を開いています。

プラガブルモジュールは依然として第一選択肢ですが、CPOがもたらす全体的なエネルギー効率の向上は、ますます多くのメーカーの注目を集めています。LightCountingによると、CPOの出荷量は800Gおよび1.6Tポートから大幅に増加し始め、2024年から2025年にかけて徐々に商用化され、2026年から2027年には大規模な量産体制に入ると予想されています。同時に、CIRは光電トータルパッケージの市場収益が2027年に54億ドルに達すると予測しています。

TSMCは今年初め、ブロードコム、NVIDIAなどの大手顧客と提携し、シリコンフォトニクス技術、共通パッケージング光学部品CPOなどの新製品、45nmから7nmまでのプロセス技術を共同開発すると発表し、最も早いのは来年後半に大規模な注文に対応し始め、2025年頃には量産段階に達すると述べた。

CPO技術は、光子デバイス、集積回路、パッケージング、モデリング、シミュレーションなどを含む学際的な技術分野であり、光電子融合がもたらす変化を反映しており、データ伝送にもたらされる変化は間違いなく破壊的なものです。CPOの応用は長い間、大規模データセンターに限られていましたが、大規模なコンピューティング能力と高帯域幅の要件がさらに拡大するにつれて、CPO光電共シール技術は新たな戦場となっています。

CPOに取り組んでいるメーカーは、2025年が重要なノードであり、交換レートが102.4Tbpsに達するノードでもあると一般的に考えていることが分かります。これにより、プラグ型モジュールのデメリットがさらに増幅されます。CPOの応用はゆっくりと進むかもしれませんが、光電子共同パッケージングは、高速、高帯域幅、低消費電力のネットワークを実現する唯一の方法であることは間違いありません。

投稿日時: 2024年4月2日